Счетчики обратного счета (вычитающие счетчики). Пусть первоначальное состояние всех триггеров счётчика будет нулевым. Его ещё называют «-1″, так как при подаче на этот вход импульсов, содержимое счётчика уменьшается на единицу. В счётчиках с обратной связью исключаются последние состояния двоичного счётчика.

Счетчики обратного счета (вычитающие счетчики). Пусть первоначальное состояние всех триггеров счётчика будет нулевым. Его ещё называют «-1″, так как при подаче на этот вход импульсов, содержимое счётчика уменьшается на единицу. В счётчиках с обратной связью исключаются последние состояния двоичного счётчика.

На базе счетных триггеров можно построить цифровое устройство, получившее название электронного счетчика. Цифровые последовательностные устройства, выполненные по схеме счетчика, но имеющие один счетный вход и один выход называются делителями частоты. Таким образом, любой счетчик может служить в качестве делителя частоты, если используется информация только одного из его выходов. Так как счетчики и делители имеют единую структуру, основное внимание будет уделено синтезу счетчиков.

Параллельные счетчики имеют более высокую скорость счета, чем асинхронные. В качестве разрядных триггеров счетчиков и делителей могут быть использованы двухступенчатые D-триггеры, Т- и JK-триггеры. Счетчики относятся к последовательностным устройствам с циклически повторяющейся последовательностью состояний. В общем случае для n — разрядного счетчика — М = 2n. Модуль счета счетчика численно совпадает с модулем деления делителя частоты.

Входы D0 … D3 предназначены для записи произвольного двоичного числа в счётчик

Как видно из рис. 3.33, (а), синхронизирующие входы всех триггеров, кроме крайнего левого (Т1), соединены с выходами предыдущих триггеров. На рис. 3.34 приведена схема асинхронного трехразрядного двоичного вычитающего счетчика, построенного на базе D-триггеров.

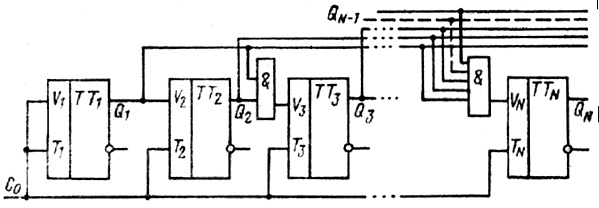

Одна из схем счётчика, с возможностью параллельной записи двоичных кодов во внутренние триггеры счётчика, приведена на рисунке 1. В этой схеме вход C предназначен для подачи тактовых импульсов

Реверсивные счетчики могут быть как асинхронного, так и синхронного типа. Они строятся путем применения логических коммутаторов (мультиплексоров) в цепях связи между триггерами. Как было уже сказано выше, параллельные счетчики бывают двух типов: синхронные параллельные и синхронные последовательные.

Рассмотрим пример реализации счетчика с Ксч=10 методом автосброса. Подобный прием удобно применять при использовании счетчиков в интегральном исполнении, имеющих ячейки конъюнкции (И) на входах установки в нуль, как это сделано в микросхеме К1533ИЕ5.

В таблице 3.1 поясняются конфигурации соединений для получения различных коэффициентов пересчета с помощью счетчика К1533ИЕ5. Анализ таблицы позволяет установить те переходы, которые должны быть “сделаны” триггерами, входящими в состав счетчика.

В правой части таблицы 3.2 приведены значения входных сигналов четырех триггеров. Для поиска этих значений должны быть проанализированы реализованные переходы, а затем с помощью управляющей таблицы (см. рис. 3.15, а) определены соответствующие значения “J” и “K” входов триггеров. На рис. 3.40 показана схема двоично-десятичного синхронного счетчика. Счётчики используются для построения схем таймеров или для выборки инструкций из ПЗУ в микропроцессорах.

При использовании в цепи ФАП счётчики могут быть использованы для умножения частоты как в синтезаторах, так и в микропроцессорах. Простейший вид счётчика — двоичный может быть построен на основе T-триггера.

В этом случае можно использовать выходной сигнал первого счетного триггера как входной сигнал для следующего триггера, то есть соединить триггеры последовательно. Запишем его в таблицу 1. После поступления на вход счётчика тактового импульса (который воспринимается по заднему фронту) первый триггер изменяет своё состояние на противоположное, то есть единицу.

Так как по приходу первого импульса изменилось состояние первого триггера, то этот триггер содержит младший разряд двоичного числа (единицы). Подадим на вход счётчика ещё один тактовый импульс. На этот раз на выходе первого триггера, а значит и на входе второго триггера сформируется задний фронт. Это означает, что второй триггер тоже изменит своё состояние на противоположное.

Это состояние иногда называют исходным состоянием счётчика. Классическим примером такого счётчика является микросхема 555ИЕ5. Счётчики могут не только увеличивать своё значение на единицу при поступлении на счётный вход импульсов, но и уменьшать его. Такие счётчики получили название вычитающих счётчиков.

В схеме, приведенной на рисунке 6, для реализации вычитающего счётчика сигнал на входы последующих триггеров подаются с инверсных выходов предыдущих триггеров. Это вызвано тем, что при поступлении переднего фронта тактового импульса первый триггер переходит в единичное состояние. В результате на его выходе тоже формируется передний фронт. Он поступает на вход второго триггера, что приводит к записи единицы и в этот триггер.

Это реверсивный счетчик-делитель на 16 с возможностью предустановки

Следующий тактовый импульс приведёт к изменению состояния только первого триггера, так как при этом на его выходе сформируется задний фронт сигнала. Запишем и это состояние в таблицу 2. Обратите внимание, что при поступлении каждого последующего импульса содержимое счётчика, построенного по анализируемой схеме, уменьшается на единицу.

Счетчики, в которых от каждого тактового импульса происходит увеличение его содержимого на единицу, называются счетчиками с прямым счетом. От сюда следует, что по спаду первого же импульса на входе С, триггер установится в единичное состояние.