Если HI=HI–1=1 и при этом существует сигнал переноса PIиз предыдущего в i-й разряд, то перенос производится сразу в i+2 разряд. Многоразрядные АЛУ выпускаются в виде интегральных микросхем или входят в состав процессоров, являясь их основой.

Если HI=HI–1=1 и при этом существует сигнал переноса PIиз предыдущего в i-й разряд, то перенос производится сразу в i+2 разряд. Многоразрядные АЛУ выпускаются в виде интегральных микросхем или входят в состав процессоров, являясь их основой.

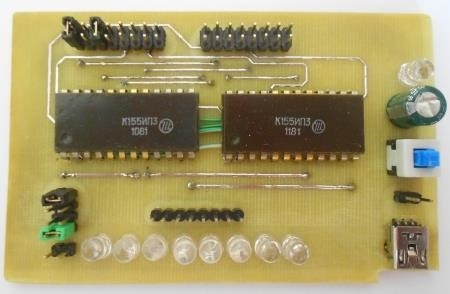

Микросхема К155ИП3, КМ155ИП3 (74181) — четырехразрядное, скоростное АЛУ. Оно может работать в двух режимах, выполняя либо 16 логических, либо 16 арифметических операций. Результат выполнения одной из 32 выбранных функций АЛУ появляется на выходах F0 — F3 (активные уровни — низкие). Этот сигнал подается на вход Сn следующего АЛУ при составлении схем АЛУ большей емкости.

При напряжении низкого уровня на входе М переносы разрешаются и будут выполняться арифметические операции над двумя четырехразрядными словами. Один корпус К155ИП4 может обслуживать четыре АЛУ К155ИП3, КМ155ИП3. Этот выход применяется для отображения логической эквивалентности четырехбитных слов, если АЛУ работает в режиме вычитания. Арифметическое-логическое устройство может работать с высокими или низкими активными логическими уровнями.

В этом случае будет производиться операция суммирования. В этом случае один из операндов поступает на вход сумматора через блок инверторов. Эти операции позволяют легко организовывать циклы в программе и переходить от предыдущего операнда к следующему. При небольшом изменении схемы такое устройство может быть преобразовано в схему, которая позволяет осуществлять не только арифметические, но и логические операции.

На уровне логических схем АЛУ состоит из логических элементов, сумматоров, триггеров и некоторых других элементов

Эта управляющая цепь обычно называется M. Подобная схема реализована в микросхеме АЛУ К155ИП3 (иностранный аналог 74181). Арифметико-логические устройства позволяют выбирать вид выполняемой операции при помощи кода, подаваемого на специальные выводы микросхемы.

В цифровой вычислительной технике используются одноразрядные суммирующие схемы с двумя и тремя входами, причём первые называются полусумматорами, а вторые — полными одноразрядными сумматорами. Быстродействие определяется суммарным временем задержки сигнала при прохождении элементов схемы. В приведённой выше схеме быстродействие определяется задержкой в трёх логических элементах.

Рис. D.1.4. Схема реализации T-триггера

Недостатком схемы рисунок 21, в) является то, что на её входы необходимо подавать и прямые и инверсные значения операндов. Представляется целесообразным разработка сумматора как устройства, имеющего три входа и два выхода. При последовательном суммировании используется один сумматор, общий для всех разрядов (Рисунок 24, а). Операнды должны вводиться в сумматор через входы аI и bI синхронно, начиная с младших разрядов.

Для увеличения разрядности обрабатываемых слов МС АЛУ можно соединять последовательно, как и в параллельных сумматорах с последовательным переносом

Слагаемые aI и bI суммируются во всех разрядах одновременно, а перенос PI поступает с окончанием операции сложения в предыдущем разряде. Блоки ускоренного переноса выпускаются в интегральном исполнении в виде отдельных микросхем или непосредственно со схемой сумматора или арифметико-логического устройства в одной микросхеме. Для выполнения операции вычитания, при использовании дополнительного кода, вычитаемое следует перевести в дополнительный код и просуммировать с первым слагаемым.

Таким образом, с выходов 1, 2, 4, 8 можно снять прямой код, соответствующий номеру входа, на который подан входной сигнал

В рассмотренной выше схеме выходной код «000» будет присутствовать на выходе при подаче сигнала на вход X0 и в случае, если входной сигнал вообще не подаётся ни на один из входов. В общем случае на информационные входы можно подавать не постоянные логические уровни, тогда на выходе мультиплексора реализуется логическая функция с большим числом переменных.

Устройства сравнения кодов предназначены для выработки выходного сигнала в случае, когда поступающие на их входы коды двух чисел оказываются одинаковыми. Для этой цели в МС К561ИП2 предусмотрены три дополнительных входа: A > B, A = B и A > B, к которым подводятся соответствующие выходы микросхемы, выполняющей сравнение младших разрядов.

По своей структуре преобразователи кодов являются дешифраторами, только они преобразуют двоичный код в сигналы не только на одном, но и на нескольких выходах. Триггер переходит из одного устойчивого состояния в другое при воздействии некоторого входного сигнала.

На входе Сn принимается входной сигнал переноса. На выходе выделяется сигнал переноса (после четырех разрядов). Выходы G и P имеют активные низкие уровни. Если от многокорпусного АЛУ не требуется максимальное быстродействие, можно использовать простой режим пульсирующего переноса.

На выходе компаратора, т.е. на выходе отображении эквивалентности А=В, будет напряжение высокого уровня, если на всех четырех выходах F оказались высокие логические уровни.

В зависимости от этого меняются знаки инверсии на входах и выходах , а также получаются различные таблицы соответствия логических и арифметических функций кодам выбора функции, (входы S0—S3). В таблице приведены аналогичные данные для активных низких уровней.

При обратном преобразовании дополнительного кода в прямой результат следует также проинвертировать и к младшему разряду добавить единицу. Логический элемент – электронная схема, реализующая элементарную переключающую функцию.